Table of Contents

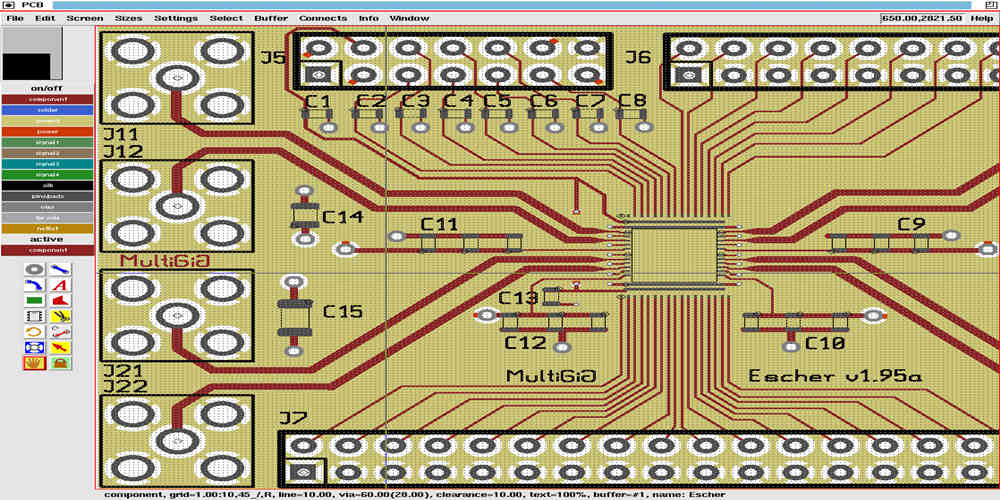

ToggleDDR3 PCB layout is a critical aspect of designing and producing DDR3 memory modules. The layout of the PCB can significantly impact the performance and reliability of the memory module. DDR3 PCB layout involves the placement and routing of the traces, vias, and components on the PCB.

One of the primary considerations in DDR3 PCB layout is signal integrity. The layout must ensure that the signals are transmitted with minimal distortion and interference. This requires careful attention to the placement and routing of the traces, as well as the use of proper termination and decoupling techniques. Another critical factor is power integrity, which involves ensuring that the power supply to the memory module is stable and free from noise and voltage fluctuations.

Basic Principles

DDR3 Memory Basics

DDR3 memory is a type of synchronous dynamic random-access memory (SDRAM) that is commonly used in modern computers. It has a higher bandwidth and lower power consumption than its predecessor, DDR2. DDR3 memory uses a double data rate (DDR) interface, which means it can transfer data on both the rising and falling edges of the clock signal.

DDR3 memory modules have a number of important specifications that must be considered when designing a PCB layout. These include the clock frequency, the data rate, the number of ranks, the number of banks, and the module density. It is important to choose memory modules that are compatible with the motherboard and processor that will be used in the system.

PCB Layout Guidelines

The PCB layout for DDR3 memory must be carefully designed to ensure reliable operation. There are several important guidelines that should be followed when designing a PCB layout for DDR3 memory:

- The routing of the clock and address lines should be kept as short as possible to minimize signal skew.

- The data lines should be routed in groups of four or eight to ensure proper termination and impedance matching.

- The power and ground planes should be designed to provide a low-impedance path for the high-speed signals.

- The signal traces should be routed with controlled impedance to minimize reflections and signal loss.

- The memory modules should be placed as close to the processor as possible to minimize signal delay.

In addition to these guidelines, it is important to follow the specific recommendations of the memory module manufacturer and to use a high-quality PCB fabrication process. By following these guidelines, it is possible to design a reliable and high-performance PCB layout for DDR3 memory.

Design Considerations

Signal Integrity

Signal integrity is a critical aspect of DDR3 PCB layout. The goal is to maintain signal integrity and minimize signal noise and crosstalk. To achieve this, it is recommended to use controlled impedance traces, avoid sharp bends and corners, and minimize the length of vias. It is also important to ensure that the signal traces are properly terminated and that the differential pairs are routed together and matched in length.

Power Delivery Network

The power delivery network is another important aspect of DDR3 PCB layout. It is important to ensure that the power and ground planes are properly connected and that there are no gaps or voids in the planes. It is also recommended to use multiple power and ground planes to reduce noise and improve the overall performance of the system.

Clock Routing

The clock signals are critical for the proper operation of the DDR3 memory. It is important to ensure that the clock signals are routed with minimal skew and that the clock traces are matched in length. It is also recommended to use a separate clock plane to reduce noise and improve signal integrity.

Trace Length Matching

The trace length matching is critical for DDR3 memory operation. It is important to ensure that the data and address signals are properly matched in length to minimize skew and ensure that the data is properly sampled by the memory controller. It is also recommended to use a serpentine routing pattern to ensure that the traces are properly matched in length.

Component Placement

The placement of components is also critical for DDR3 PCB layout. It is important to ensure that the memory chips are properly placed and oriented to minimize noise and crosstalk. It is also recommended to keep the memory chips as close as possible to the memory controller to minimize signal loss and improve signal integrity.

In summary, DDR3 PCB layout requires careful consideration of signal integrity, power delivery network, clock routing, trace length matching, and component placement. By following these guidelines, designers can ensure that their DDR3 memory systems operate reliably and efficiently.

Testing and Validation

When designing a DDR3 PCB layout, testing and validation are critical steps to ensure proper functionality and reliability of the system. In this section, we will discuss the various simulation tools and analysis techniques used for testing and validation.

Simulation Tools

Simulation tools are essential for testing and validating DDR3 PCB layouts. These tools allow designers to simulate the behavior of the system before it is manufactured, which helps identify and correct any potential issues early in the design process.

One commonly used simulation tool is SPICE (Simulation Program with Integrated Circuit Emphasis). SPICE simulates the electrical behavior of circuits and provides accurate predictions of circuit performance.

Signal Integrity Analysis

Signal integrity analysis is another critical step in testing and validating DDR3 PCB layouts. Signal integrity refers to the ability of a signal to propagate through a circuit without distortion or loss.

Signal integrity analysis tools, such as HyperLynx, can be used to analyze signal quality and identify any potential issues. These tools can also simulate the effects of various signal parameters, such as rise and fall times, on the circuit’s performance.

Power Integrity Analysis

Power integrity analysis is also an important part of testing and validating DDR3 PCB layouts. Power integrity refers to the ability of a power supply to deliver clean and stable power to the circuit.

Power integrity analysis tools, such as PowerSI, can be used to analyze the power delivery network and identify any potential issues. These tools can also simulate the effects of various power parameters, such as voltage drop and noise, on the circuit’s performance.

In conclusion, testing and validation are critical steps in ensuring proper functionality and reliability of DDR3 PCB layouts. Simulation tools, signal integrity analysis, and power integrity analysis are all essential techniques used to identify and correct any potential issues early in the design process.