Table of Contents

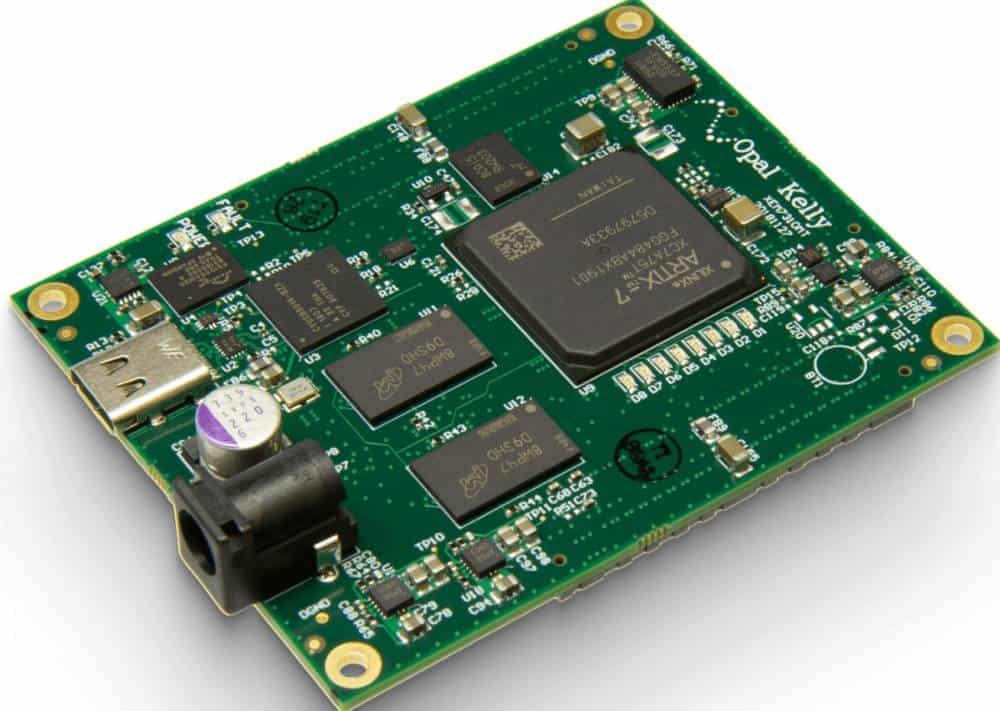

ToggleThe optimization of the Xilinx XA Artix-7 FPGAs is done for the lowest power and cost with a packaging of small form-factor for automotive applications of high volume. Furthermore, designers have the ability to leverage extra or more logic for each watt in contrast to the Xilinx Spartan-6 FPGA family.

The Xilinx XA Artix-7 FPGAs are built on a low-power/high-performance 28 nm metal gate process technology. This is how the Xilinx XA Artix-7 FPGAs help in redefining alternatives of low-cost with more logic for each watt.

This Xilinx XA Artix-7 FPGAs has an unparalleled increase in the performance of the system with a 52 Gb/s Input/Output bandwidth, 264 GMAC/s DSP, a logic cell capacity of 100,000, and in-built flexible DDR3 memory interfaces which makes it possible for low-cost, high-throughput automotive applications.

Furthermore, the Xilinx XA Artix-7 FPGAs come with lots of high-end features, like AMS (Analog Mixed Signal) technology, which are integrated and advanced. Also, Analog has now become the next integration level via the implementation of 1 MSPS, dual 12-bit, analog-to-digital converters of 17 channels.

Also, which is very important, the Xilinx XA Artix-7 FPGAs meet the automotive grade’s high standards with 125°C as the maximum temperature.

Configurable Logic Blocks, LUTs and Slices

Some of the major features of the architecture of configurable logic blocks are:

- Shift register and register functionality

- Memory capability in the look-up tables (LUT)

- 6-input LUTs

You can configure the LUTs found in the Xilinx XA Artix-7 FPGAs either as 6-input look-up tables having one output, or like two 5-input look-up tables of 32-bit ROMs. Having separate outputs, however with common logic inputs or addresses.

Optionally, you can register each look up table in a flip-flop. Furthermore, four of such look up tables with their 8 flip-flops, coupled with arithmetic carry logic and multiplexers usually make up a slice, while a configurable logic block is formed by two slices. Four out of the 8 flip-flops for each slice (one for each look-up table) can be configured like latches optionally.

About 25 to 50% of the slices have the ability to utilize their Look-up tables as distributed 32-bit or 64-bit RAM shift registers. Furthermore, it can also function as two main SRL16s.

Furthermore, modern tools for synthesis capitalize on these very efficient memory, arithmetic, and logic features. Now, let’s go to clock management.

——————————————————————————————————————

Request Xilinx XA Artix-7 FPGA Quote , Pls Send Files to Sales@raypcb.com Now

——————————————————————————————————————

Clock Management

Here, some major highlights of the architecture of clock management include:

- Phase shifting and frequency synthesis

- Buffers of high speed and routing for clock distribution (low-skew)

- Jitter filtering and clock generation (low-jitter)

Each of the Xilinx XA Artix-7 FPGAs has about 3 to 6 CMTs, with each being made up of one (MMCM) clock manager of mixed mode, and a single PLL (phase-locked pool).

Clock Manager (Mixed-Mode) and PLL (Phase-Locked Loop)

The PLL and MMCM have many characteristics in common. The two can function as a synthesizer of frequency for different frequencies. It also plays a vital role in incoming clocks as a jitter filter.

At the middle of the two components is a VCO, also called voltage-controlled oscillator. This VCO helps in speeding up, as well as slowing down. This depends on the voltage of the input it gets from the PFD (phase frequency detector).

Three main sets of frequency dividers are available. These are O, M, and D.

Sets of Frequency Dividers

The pre-divider, which is denoted as D (can be programmed via configuration and after through DRP) helps in reducing the frequency of the input. Furthermore, it feeds an input of the PLL phase.

For M, which is the feedback divider M (can be programmed via configuration and after through DRP) functions like a multiplier. This is due to the fact that it shares or divides the output frequency of the VCO before you go ahead to feed the phase connector’s other input.

Note that you have to choose M and D appropriately. This will help in keeping the VCO in its specific range of frequency. Also, this VCO features eight output phases with equal spacing (0 degrees, 45 degrees, 90 degrees, 135 degrees, 180 degrees, 225 degrees, 270 degrees, and 315 degrees).

You can choose each of these output phases to drive any of its output dividers, with each of them programmable via configuration. Furthermore, the PLL and MMCM features three filter options. These include optimized node, high bandwidth, or low bandwidth.

The mode with low bandwidth comes with the most effective jitter attenuation. However, it isn’t the offset of the smallest phase. Modes with high bandwidth feature the offset with the best phase. However, it doesn’t deliver the most appropriate jitter attenuation. With optimized mode, the tools will be able to find the most appropriate setting.

Other Programmable Features of the MMCM

The MMCM may feature a fractional counter in any of the feedback paths (serving as the multiplier) or in a single output path. With fractional counters, a non-integer increase of one-eighth is possible and can therefore lead to an increase in the capabilities of frequency synthesis by 8.

Furthermore, this MMCM can offer a dynamic or fixed phase shift in little increments, which depend on the frequency of the VCO. At a frequency of 1440 MHz, this increment of the phase-shift timing is 12.5 ps.

Distribution of the Clock

Each of the seven series FPGA offers six clock line types (high-performance, BUFMR, BUFH, BUFIO, BUFR, and BUFG. This helps in addressing the different requirements for clocking of very low skew, short delay in propagation, and high fanout.

Global Clock Lines

For all the Xilinx XA Artix-7 FPGAs, the highest and greatest fanout can be seen in 32 global clock lines. They can get to all the clock enable, flip-flop clock, set/reset, and clock enable, coupled with lots of logic inputs.

Furthermore, there are 12 clock lines (global) present in all clock regions, which are driven by the BUFH. You can disable or enable each of the BUFH independently, thereby permitting the turning off of clocks within the region, which eventually leads to the offering of a control over whichever clock regions takes or consume power.

You can drive clock lines (global) using clock buffers (global). This can also function in clock multiplexing, as well as functions for clock enable. Furthermore, you drive global clocks from the CMT. This can get rid of the basic delay in clock distribution completely.

Regional Clocks

With regional clocks, it is possible to drive all the destinations of the clock in their specific region. The Xilinx XA Artix-7 FPGAs possess between 6 to 8 regions. For every region, four clock tracks (regional) are present.

You can drive each of the buffers of the regional clocks. This can be done from any of four input pins (clock-capable). You can divide its frequency optionally by integers between 1 and 8.

Input/Output (I/O) Clocks

The input/output clocks are very fast and will only serve serializer/deserializer and I/O logic circuits. The devices of the Xilinx XA Artix-7 FPGAs connect directly from the MMCM to the Input/Output for high-performance, low-jitter interfaces.

Block RAM

Below are the major features of a block RAM:

- FIFO logic that is programmable

- Dual-port block RAM of 36 Kb

- In-built optional circuitry for error correction

Note that the Xilinx XA Artix-7 FPGAs have about 20 to 135 block RAMs with dual ports. Each of these stores is about 36 Kb. Furthermore, each of the block RAMs have two independent ports, which share only the data stored.

Synchronous Operation

The clock controls each memory write, read, or access. Also, all the data, inputs, address, write enable, and clock enables are registered. Virtually, nothing can happen without using a clock. Furthermore, the address for the input is clocked at all times.

This helps in retaining all the data till you are ready for another operation. With an optional pipeline register for output data, it is possible to have higher rates of clocks at an extra latency cycle.

Furthermore, when performing a write operation, this data output has the ability to reflect either the data you have stored previously, the data you have just written, or can stay without any change.

Detection and Correction of Error

With each block RAM with width of 64-bit, it is possible to create, store, and use eight extra bits of hamming code and carry out both single-bit and double-bit correction of error during the process of reading. Furthermore, you can also use the ECC logic when reading from or writing to external memories with width falling between 64- and 72-bit.

FIFO Controller

Here, the in-built FIFO controller for dual-clock or single-clock operation increases the internal addresses. Furthermore, it offers four major handshaking flags. These include almost empty, almost full, empty, and full.

For the almost empty and almost full flags, they are programmable. Just like the block RAM, you can program the depth and width of the FIFO; however, the read and write ports always possess similar or identical widths.

——————————————————————————————————————

Request Xilinx XA Artix-7 FPGA Quote , Pls Send Files to Sales@raypcb.com Now

——————————————————————————————————————

What are the Devices of the Xilinx XA Artix-7 FPGAs?

There are 36 devices for the Xilinx XA Artix-7 FPGAs

XA7A75T-2FGG484I XA7A75T-1FGG484Q XA7A75T-2CSG324I

XA7A75T-1FGG484I XA7A75T-1CSG324I XA7A75T-1CSG324Q

XA7A50T-2CSG325I XA7A50T-1CSG325Q XA7A50T-2CPG236I

XA7A50T-1CSG325I XA7A50T-1CSG324I XA7A50T-1CSG324Q

XA7A50T-1CPG236Q XA7A35T-2CSG325I XA7A50T-1CPG236I

XA7A35T-2CSG324I XA7A35T-1CSG325Q XA7A35T-2CPG236I

XA7A35T-1CSG325I XA7A35T-1CSG324I XA7A35T-1CSG324Q

XA7A35T-1CPG236Q XA7A15T-2CSG324I XA7A15T-2CSG325I

XA7A15T-1CSG325Q XA7A15T-1CSG324I XA7A15T-1CSG324Q

XA7A15T-1CPG236Q XA7A100T-2FGG484I XA7A15T-1CPG236I

XA7A100T-2CSG324I XA7A100T-1CSG324I XA7A100T-1FGG484I

XA7A100T-1FGG484Q XA7A50T-2CSG324I XA7A100T-1CSG324Q

Features of the Devices of the Xilinx XA Artix-7 FPGAs

XA7A75T-2FGG484I

Features of the XA7A75T-2FGG484I

Advanced FPGA logic with high-performance based on the real lookup table technology with 6-input configurable like distributed memory. Also it has a dual-port 36 Kb block RAM having in-built FIFO logic to serve data buffering (on-chip)

SelectIO technology has high-performance DDR3 interfaces support to reach 1,866 Megabytes per second. Also present, is a serial connectivity of high speed with multi-gigabit in-built transceivers from 600 megabytes per second to high and maximum rates of 6.6 Gigabytes per second up to 28.05 Gigabytes per second, and providing a low-power mode, with optimization done for any chip-to-chip interface.

Also present is an analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors. Furthermore, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering.

Powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision. Also, there are different configuration options, which include commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection. Lastly, it is w32ell designed to deliver the lowest power and for high performance

XA7A75T-1FGG484Q

Features of XA7A75T-1FGG484Q

It has SelectIO technology having high-performance with DDR3 interfaces support to reach 1,866 Megabytes per second. Well designed to deliver the lowest power and for high performance.

Also present is a Serial connectivity of high speed with multi-gigabit in-built transceivers from 600 megabytes per second to high and maximum rates of 6.6 Gigabytes per second up to 28.05 Gigabytes per second, and providing a low-power mode, with optimization done for any chip-to-chip interface.

Furthermore, there is analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors.

In addition, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering. Advanced FPGA logic with high-performance based on the real lookup table technology with 6-input configurable like distributed memory

Dual-port 36 Kb block RAM having in-built FIFO logic to serve data buffering (on-chip. Different configuration options, which includes commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection.

Lastly, this device has a powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision.

XA7A75T-2CSG324I

Features of XA7A75T-2CSG324I

This device is properly designed to deliver the lowest power and for high performance

Powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision. Different configuration options, which includes commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection.

Advanced FPGA logic with high-performance based on the real lookup table technology with 6-input configurable like distributed memory

Serial connectivity of high speed with multi-gigabit in-built transceivers from 600 megabytes per second to high and maximum rates of 6.6 Gigabytes per second up to 28.05 Gigabytes per second, and providing a low-power mode, with optimization done for any chip-to-chip interface.

SelectIO technology having high-performance with DDR3 interfaces support to reach 1,866 Megabytes per second. Dual-port 36 Kb block RAM having in-built FIFO logic to serve data buffering (on-chip)

Also present is analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors. Furthermore, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering.

XA7A75T-1FGG484I

Features of XA7A75T-1FGG484I

This device has a Serial connectivity of high speed with multi-gigabit in-built transceivers from 600 megabytes per second to high and maximum rates of 6.6 Gigabytes per second up to 28.05 Gigabytes per second, and providing a low-power mode, with optimization done for any chip-to-chip interface.

Advanced FPGA logic with high-performance based on the real lookup table technology with 6-input configurable like distributed memory. Dual-port 36 Kb block RAM having in-built FIFO logic to serve data buffering (on-chip). SelectIO technology having high-performance with DDR3 interfaces support to reach 1,866 Megabytes per second.

For this device, there are different configuration options, which includes commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection. Powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision.

Also present is analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors. Furthermore, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering.

XA7A75T-1CSG324I

Features of XA7A75T-1CSG324I

This device features an analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors.

Advanced FPGA logic with high-performance based on the real lookup table technology with 6-input configurable like distributed memory. It is Well designed to deliver the lowest power and for high performance

Furthermore, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering. Dual-port 36 Kb block RAM having in-built FIFO logic to serve data buffering (on-chip)

SelectIO technology having high-performance with DDR3 interfaces support to reach 1,866 Megabytes per second. Powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision.

Different configuration options, which includes commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection.

XA7A75T-1CSG324Q

Features of XA7A75T-1CSG324Q

This Xilinx XA Artix-7 FPGAs device has a serial connectivity of high speed with multi-gigabit in-built transceivers from 600 megabytes per second to high and maximum rates of 6.6 Gigabytes per second up to 28.05 Gigabytes per second, and providing a low-power mode, with optimization done for any chip-to-chip interface.

Dual-port 36 Kb block RAM having in-built FIFO logic to serve data buffering (on-chip). Furthermore, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering

Also present, is an analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors. Advanced FPGA logic with high-performance based on the real lookup table technology with 6-input configurable like distributed memory

SelectIO technology having high-performance with DDR3 interfaces support to reach 1,866 Megabytes per second. Powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision.

Different configuration options, which includes commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection.

XA7A50T-2CSG325I

Features of XA7A50T-2CSG325I

Powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision. Furthermore, it is well designed to deliver the lowest power and for high performance

Advanced FPGA logic with high-performance based on the real lookup table technology with 6-input configurable like distributed memory. Also, there are different configuration options, which include commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection.

Dual-port 36 Kb block RAM having in-built FIFO logic to serve data buffering (on-chip). Also, there is SelectIO technology having high-performance with DDR3 interfaces support to reach 1,866 Megabytes per second.

Serial connectivity of high speed with multi-gigabit in-built transceivers from 600 megabytes per second to high and maximum rates of 6.6 Gigabytes per second up to 28.05 Gigabytes per second, and providing a low-power mode, with optimization done for any chip-to-chip interface.

Also present is analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors. Furthermore, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering.

——————————————————————————————————————

Request Xilinx XA Artix-7 FPGA Quote , Pls Send Files to Sales@raypcb.com Now

——————————————————————————————————————

XA7A50T-1CSG325Q

Features of XA7A50T-1CSG325Q

There is an advanced FPGA logic with high-performance based on the real lookup table technology with 6-input configurable like distributed memory. Furthermore, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering.

Furthermore, there is a SelectIO technology having high-performance with DDR3 interfaces support to reach 1,866 Megabytes per second. Also present is analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors.

Powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision. Different configuration options, which includes commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection.

XA7A50T-2CPG236I

Features of XA7A50T-2CPG236I

This device is well designed to deliver the lowest power and for high performance. First, it has dual-port 36 Kb block RAM having in-built FIFO logic to serve data buffering. SelectIO technology having high-performance with DDR3 interfaces support to reach 1,866 Megabytes per second.

Serial connectivity of high speed with multi-gigabit in-built transceivers from 600 megabytes per second to high and maximum rates of 6.6 Gigabytes per second up to 28.05 Gigabytes per second, and providing a low-power mode, with optimization done for any chip-to-chip interface.

Also present is analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors. Advanced FPGA logic with high-performance based on the real lookup table technology.

Furthermore, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering. Different configuration options, which includes commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection.

Powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision.

XA7A50T-1CSG325I

Features of XA7A50T-1CSG325I

Here, there is an analog interface that is user configurable, which incorporates a 12-bit dual 1MSPS analog to digital converters with on-chip supply and thermal sensors. Also present are advanced FPGA logic with high-performance based on the real lookup table technology with 6-input configurable like distributed memory.

Serial connectivity of high speed with multi-gigabit in-built transceivers from 600 megabytes per second to high and maximum rates of 6.6 Gigabytes per second up to 28.05 Gigabytes per second, and providing a low-power mode, with optimization done for any chip-to-chip interface.

Powerful CMT (clock management tiles), that combines phase-locked loop coupled with MMCM blocks to ensure low jitter and high precision. Furthermore, there are DSP slices featuring a 48-bit accumulator, a 25 x 18 multiplier, as well as a pre-adder. This is to ensure high filtering, which includes optimized coefficient filtering.

Different configuration options, which includes commodity memories support, AES encryption of 256-bit, and an in-built SEU correction and detection. Well designed to deliver the lowest power and for high performance.

Conclusion

We believe we have been able to explain in detail what the Xilinx XA Artix-7 FPGAs are. To remind us, this family is done for the lowest power and cost with a packaging of small form-factor for automotive applications of high volume. Also, the Xilinx XA Artix-7 FPGAs possess 36 devices, and they all have their individual features. If after going through this article, you have some questions you need answers to, do well to reach out to us. We will do our best to provide answers to your questions.